Exam.Code:0929 Sub. Code: 6597

## 2122

## B.E. (Electronics and Communication Engineering) Fifth Semester

EC-505: Digital System Design

Time allowed: 3 Hours Max. Marks: 50

NOTE: Attempt <u>five</u> questions in all, including Question No. I which is compulsory and selecting two questions from each Part.

x-x-x

| ı. |    | 그 사람들은 사람들이 가지 않는 것을 하면 하는 것으로 가지 않는데 가지 않는데 살아 있다.             |     |

|----|----|-----------------------------------------------------------------|-----|

|    | a) | What are multi output functions? Explain with an example.       | (2) |

|    | b) | Explain state assignment with the help of an example.           | (2) |

|    | c) | Explain block parity method for error detection and correction. | (2) |

|    | d) | Explain stuck-at-zero and stuck-at-one faults.                  | (2) |

|    | e) | What is the difference between critical and non-critical races? | (2) |

|    |    |                                                                 |     |

|    |    | Part A                                                          |     |

|    |    |                                                                 |     |

2 (a) Calculate the essential prime implicants for the following using Q-M method:

| Y = ]      | $\sum m (0,2,4,7,8,16,24,32,36,40,48)$                                      | (5)         |

|------------|-----------------------------------------------------------------------------|-------------|

| (b) Mini   | mize the following using K-map:                                             |             |

| Y(A        | $(B,C,D) = \Pi M (1,2,3,8,9,10,11,14) \cdot d (7,15)$                       |             |

| Also in    | nplement the circuit using NOR gates only.                                  | (5)         |

| 3 (a)Imple | ement the following function $Y(A,B,C) = \sum_{i=1}^{n} (0,1,3,5,7)$ using: |             |

| (i)        | Type 0 Mux designing                                                        |             |

| (ii)       | Type 1 Mux designing                                                        |             |

| (iii)      | Type 2 Mux designing.                                                       | (5)         |

|            | ain error detection and correction techniques.                              | (5)         |

| 4 (a) Expl | ain path sensitizing method for fault detection in combinational circuits.  | (5)         |

| (b) Assu   | me data 1001101 as number of message bits or data bits without parity       | bits. Check |

| the erro   | r if any and find the correct code using Hamming codes.                     | (5)         |

## Part B

| 5 (a) Derive the state table and state diagram for the following                |               |

|---------------------------------------------------------------------------------|---------------|

| JA = XB', $KA = 1$ , $JB = X'A'$ , $KB = 1$ and output $Y = B' + X' + A'$ .     | 1             |

| Also specify the type of clocked sequential circuit.                            | (5)           |

| (b) Convert SR flip-flop to D flip-flop.                                        | (5)           |

| 6 (a) How hazards can be removed? Also explain cycles and hazards in asynchron  | ious          |

| circuits.                                                                       | (5)           |

| (b) What are Moore and Mealy machines? Compare the machines with the hel        | p of suitable |

| circuit diagram.                                                                | (5)           |

| 7 (a) Write all the methods for fault detection in sequential circuits. Explain | any one with  |

| suitable example.                                                               | (5)           |

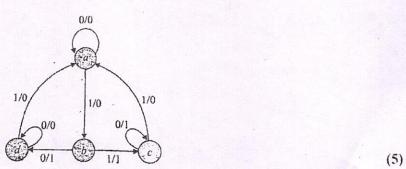

| (b) Design a circuit that will function according to the given state diagram    |               |

|                                                                                 |               |