## 1079

## B.E. (Electronics and Communication Engineering) Fifth Semester

EC-505: Digital System Design

<sub>Time allowed:</sub> 3 Hours

Max. Marks: 50

NOTE: Attempt five questions in all, including Question No. I which is compulsory and selecting two questions from each Part.

*x-x-x*

| a) Explain state assignment with the help of an example.                                                  |             |

|-----------------------------------------------------------------------------------------------------------|-------------|

| h) What are much output functions? Explain with                                                           | (2)         |

| c) Explain block parity method for error detection and correction.                                        | (2)         |

| d) Why the numbering in K-map cells are not in sequence?                                                  | (2)         |

| e) What is the difference between critical and non-critical races?                                        | (2)         |

| Post A                                                                                                    | (2)         |

| Part A                                                                                                    |             |

| Q2 (a) Minimize the following using K-map:                                                                |             |

| $Y(A,B,C,D) = \Pi M (1,2,3,8,9,10,11,14) \cdot d (7,15)$                                                  |             |

| Also implement the circuit using NOR gates only.                                                          | (5)         |

| (b) Calculate the essential prime implicants for the following using Q-M method:                          |             |

| $Y = \sum m (0,2,4,7,8,16,24,32,36,40,48)$                                                                | (5)         |

| Q3 (a)Implement the following function $Y(A,B,C) = \sum m (0,1,3,5,7)$ using:<br>(i) Type 0 Mux designing |             |

| (ii) Type 1 Mux designing                                                                                 |             |

| (iii) Type 2 Mux designing.                                                                               | (5)         |

| (b) Explain error detection and correction techniques.                                                    | (5)         |

| O4 (a) Assume data 1001101 as number of message bits or data bits without parity                          | oits. Check |

| the error if any and find the correct code using Hamming codes.                                           | (5)         |

| (b) Explain path sensitizing method for fault detection in combinational circuits.                        | (5)         |

| Part 8                                                                                                    |             |

| O5 (a) Davive the state table and state diagram for the following                                         |             |

Q5 (a) Derive the state table and state diagram for the fo JA = XB', KA = 1, JB = X'A', KB = 1 and output Y = B' + X' + A'. (5)Also specify the type of clocked sequential circuit. (b) Convert SR flip-flop to D flip-flop.

Q6 (a) How hazards can be removed? Also explain cycles and hazards in asynchronous (5)(b) What are Moore and Mealy machines? Compare the machines with the help of suitable circuits.

circuit diagram.

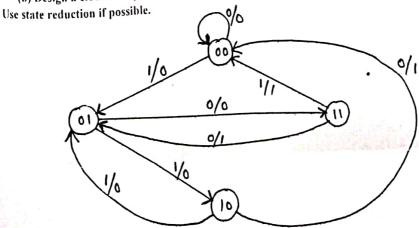

Q7 (a) Write all the methods for fault detection in sequential circuits. Explain any one with (b) Design a clocked sequential circuit using T flip-flop for the following state diagram . suitable example.

(5)